Standard Cell & I/O Library Design using MunEDA WiCkeDTM

WiCkeD for Standard & I/O Cell Design – User Benefits

- Smart, Fast, Reliable!

- Quickly detect critical transistors and non linearities vs. operating conditions

- Determine Performance Worst Case Operating Conditions for each corner

- Optimize Performance @ Nominal + Worst Case Operating Conditions & Corners!

Standard Cells

Many building blocks of memory (SRAM, DRAM, Flash, FPGA) are very sensitive to process variation, supply voltage, leakage and mismatch. Top challenge for Standard cells are group of transistors and interconnect structures that provide boolean logic funtions (e.g. AND, OR, XOR, XNOR, inverters) or a storage function (flipflop or latch). The simplest cells are direct representations of the elemental NAND, NOR, and XOR boolean function, although cells of much greater complexity are commonly used (such as a 2-bit full-adder, or muxed D-input flipflop).

Standard Cell Design Objectives & Challenges

The major objectives for the design of standard cells are:

- Optimization of standard cell main performances

- Improve Timing

- Save Power

- Analysis & Optimization of standard cell performances robustness

- Ensure immunity to process parameter variations (global & local variation, mismatch)

- Statistical Analysis

- Achieve reliable solutions for desired implementations

- Sustaining electrical constraints (multi voltage operating points, frequencies)

- Matching layout requirements (Area, DFM)

Here the standard cell designer is confronted with many challenges and decisions e.g. which performances to optimize, which constraints to apply or which design parameter to vary. Additionally he has to face also different operating parameters (voltages, temperatures, etc.), multiple process corners (SNSP, FNSP, etc.) and multiple loads or slope transitions. Further restrictions are often also simulation resources and CPU time.

Solution – MunEDA WiCkeD Analysis and Optimization for Standard Cell Design & Reliability Flow

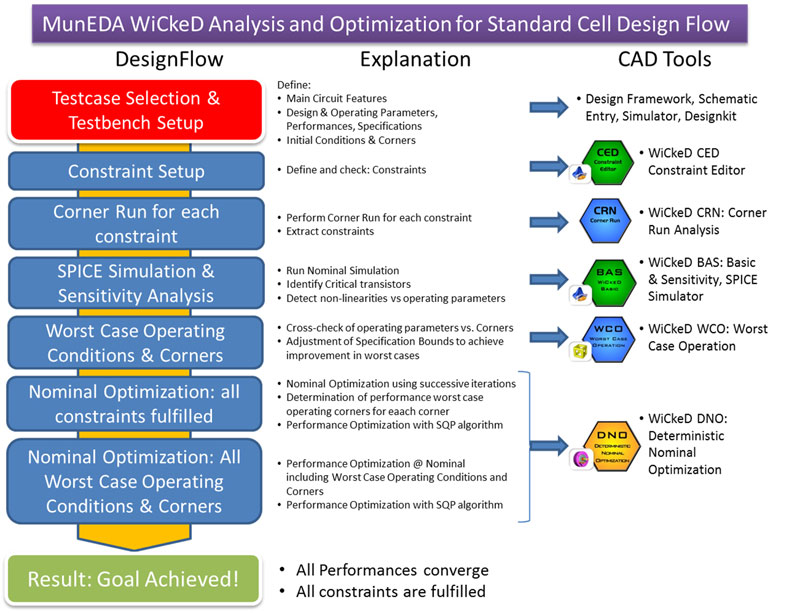

MunEDA WiCkeD Analysis and Optimization for Standard Cell Design Flow

Using different analysis and optimization tools of MunEDA WiCkeD the standard cell designer can solve many of the above described challenges. He first starts with the selection and description of the testcase including testbenches (e.g. Flip Flop, Latch, o.a.). Main circuit features are given by the circuit topology, technology and performance definitions. Using the powerful WiCkeD CED Constraint Editor the designer can add all desired netlists with one mouse-click, then define the constraints and performances and also check the initial conditions and corners. The user can with WiCkeD CRN Corner Run Analysis perform a corner run for every constraint.

After this using WiCkeD BAS Basic & Sensitivity Analysis the designer identifies critical transistors and checks non-linearities vs the defined operating parameters. With WiCkeD WCO Worst Case Operation analysis the designer then can cross-check easily the worst case performances against all operating conditions and corners. After this he can use the powerful and numerous silicon-proven optimization algorithms of WiCkeD DNO Deterministic Optimization to determine the performance worst case operating conditions for each corner and finally run performance optimization @ nominal + worst case operating conditions and corners. Goal is to converge all performances with a minimum number of iterations including the fulfilment of all constraints to guarantee a feasible solution.

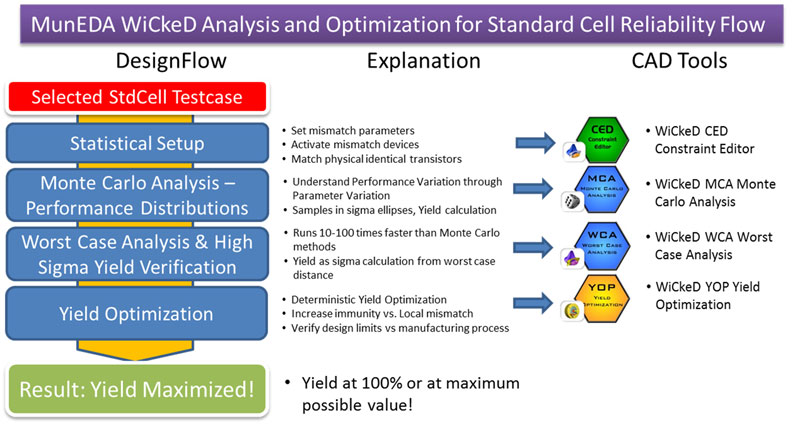

MunEDA WiCkeD for Standard Cell Reliability Flow

With MunEDA WiCkeD the standard cell designer can very easily setup his circuit for statistics and perform mismatch and yield analysis. For this reason he only has to use WiCkeD CED Constraint Editor of the already setup cell to set mismatch parameters, activate the mismatch devices and match physical identical transistors.

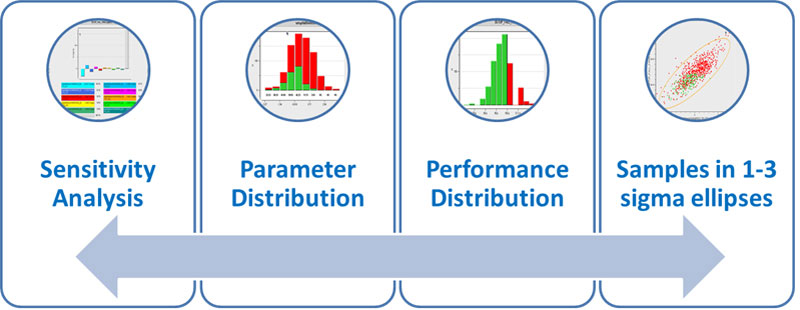

For more in-depth statistical analyses numerous powerful high-sigma analysis methods are available such as:

- Corner Run Analysis

- Monte-Carlo-Analysis

- Process Sensitivity Analysis

- Parameter Distribution

- Performance Distribution

- Parameter Sweeps

- Worst-Case Analysis & Diagnosis

- Mismatch Analysis

- and many more

WiCkeD’s unique and powerful silicon-proven YOP Yield Optimization improves yield and performance reliability to the maximum.

MunEDA WiCkeD – Technology Support

- WiCkeDTM & SPT Design Tool Suites

- Integrated into standard design environments

- For more information and support contact www.muneda.com

RacyICs at MUGM MunEDA User Group Meeting 2023

“WiCkeD binary PASS/FAIL enabled us to use unmodified extracted netlists without need for internal probing or modifications. We derived and verified additional constraints to ensure internal 6-sigma robustness for all flops @ 0.5V and 0.8V”

Let’s work together on your

next design project

Use MunEDA tools and support to speed up efficiency,

quality and outcome of your next circuit design project