High-Sigma Verification for SRAM Designs

Highlights

- Fast, efficient, cost effective

- Robust & Standard Yield Estimation

- High-Sigma Yield & Robustness Estimation

- Sampling-based and Deterministic Yield Analysis Methods

- Saves on unnecessary silicon runs

Circuit Application examples

- Memory (SRAM, DRAM, CRAM, Flash, Embedded, FPGA, etc.) – Sense Amplifier, Bit Cells, Memory Interfaces

- Standard Cells, Flip Flop, Multibit Register, Look-up Tables

- Comparator, ADC, Transceiver, Bandgap, Charge Pump

- PLL, VCO, Oscillator, Filter, OpAmp, SerDes

- … and many more

Challenges for high-sigma circuits and designs

Yield estimation, optimization and verification for high-yielding circuits such as SRAM or CRAM requiring high-sigma robustness is very challenging compared to other circuits:

- Such cells often appear by thousands or even millions on one chip

- The failure of any individual cell can result in the failure of the entire systems or chip, if no redundancy is implemented

For these cells it is critical to design cells with extremely low failure probability.

Typically a yield estimation method must be able to predict yield higher than 0.9999 -> at the tail of the distribution (>6σ for a Gaussian distribution) especially if some circuit performances (e.g. write time) show non-Gaussian distributions with long tails.

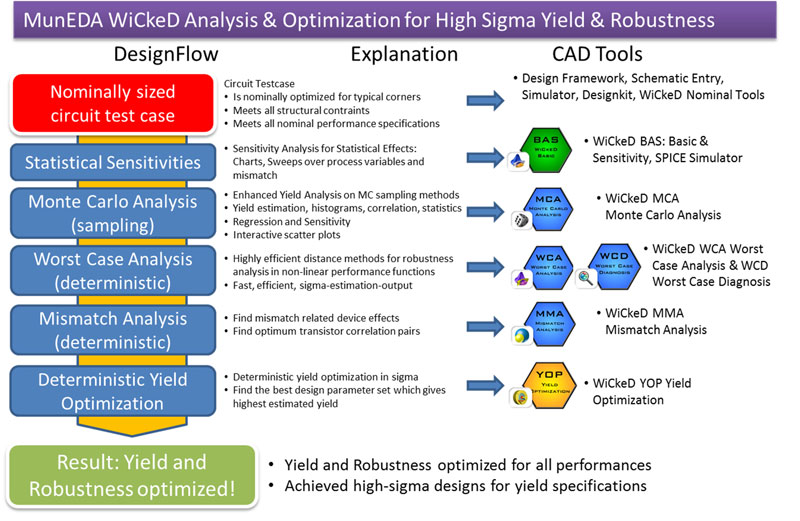

High-Sigma Estimation in WiCkeD

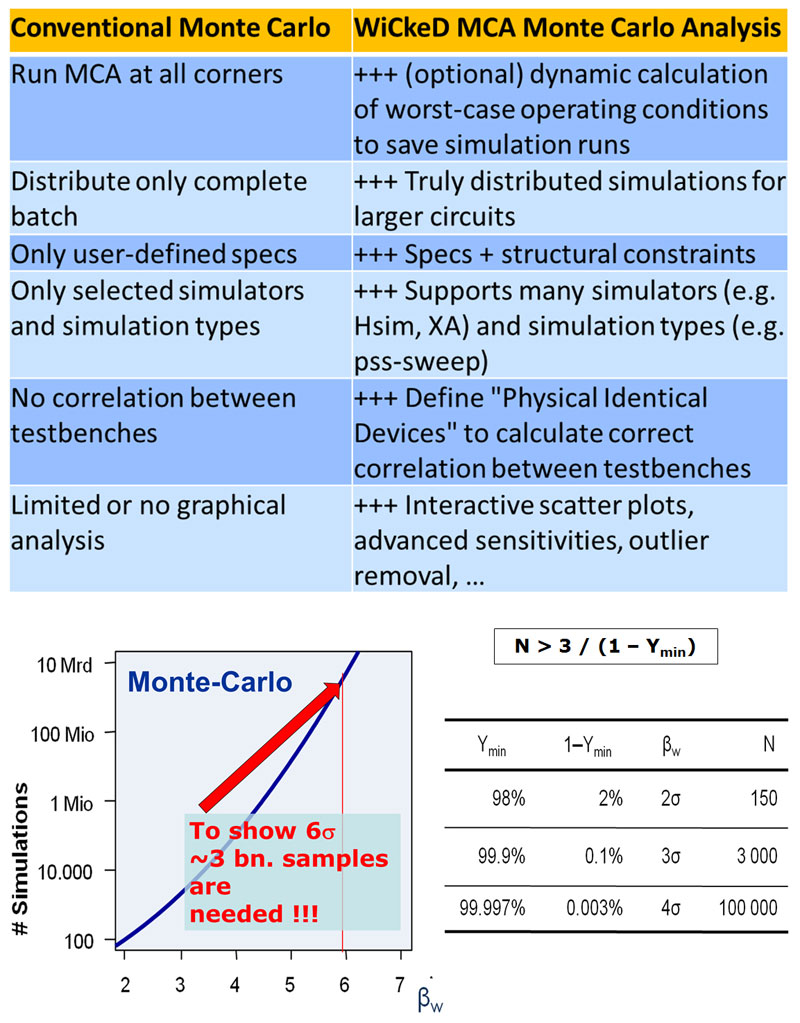

Monte Carlo Analysis

MunEDA WiCkeD includes several Monte Carlo Methods like:

- Direct Monte Carlo (DMC)

- Quasi-Monte Carlo (QMC)

- Important Sampling (IS)

Monte Carlo is seen as established and very robust yield estimation method, nevertheless all Monte Carlo Methods are limited and can not handle efficiently ultra high-sigma (>6σ) robustness analysis and not even circuit optimization tasks.

Like also described in the figures below the verification of a yield Y > Ymin with 95% confidence for counting Method DMC is because of the huge required simulation number not feasible or realistic.

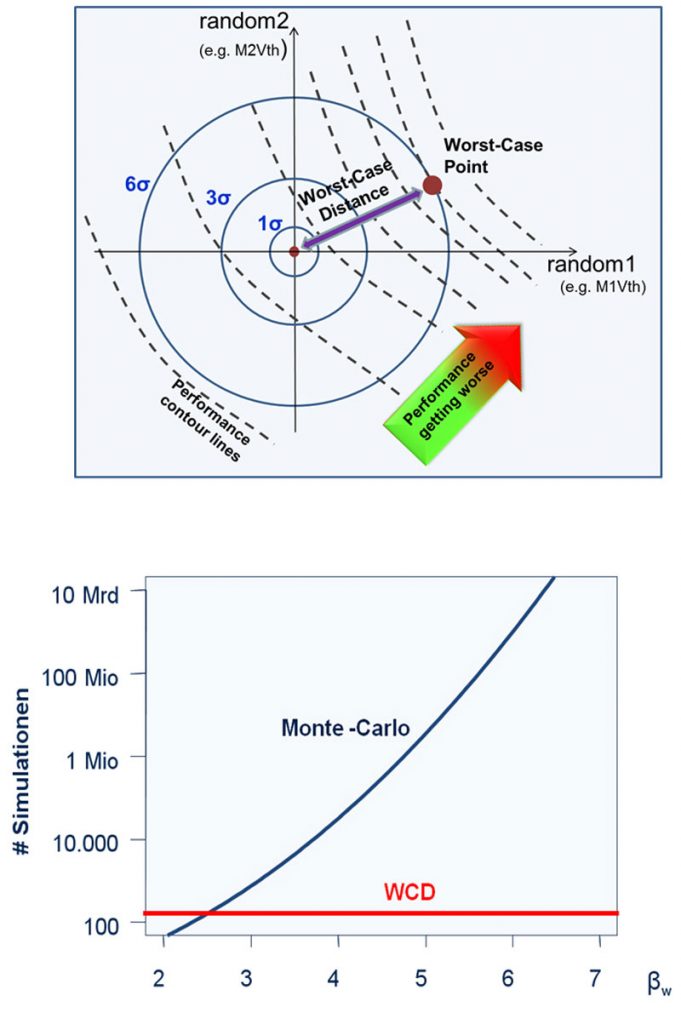

Worst Case Analysis

The Worst Case Analysis methods in WiCkeD are based on the calculation of the Worst-Case Point (WCP) and the so-called Worst-Case-Distance (WCD).

This is the point on the specification boundary closest to the mean value. In WiCkeD WCP/WCD are calculated for every parameter simultaneously to verify consistent designs.

WiCkeD Worst-Case Analysis (WCA):

- Finds the combination of process parameter values that is most likely to violate the spec -> base for Yield Analysis

- WCA is efficient and can handle non-Gaussian specs with long tails

- The effort grows only linearly with the number of process parameters

- Can handle >6 sigma and higher robustness measures easily

- Needs much fewer samples compared to Monte Carlo Methods

- WCA/WCD results can be used efficiently for Robustness & Yield Optimization

Sensitivity Analysis

With WiCkeD BAS Sensitivity Analysis Designers can do sensitivity calculation (e.g. geometries, process, operating conditions, mismatch) and sweeps for all kinds of analyses (DC, AC, Tran, RF, …) using all kind of industrial SPICE/FastSPICE simulators. The sweeps include constraint violation markers to verify designs will not be violated.

Mismatch Analysis

The WiCkeD deterministic mismatch analysis MMA identifies and analyses mismatch-relevant transistor pairs on selected circuit performances.

The variance of these local variations will be analyzed based on dependencies of device pair geometries.

MunEDA WiCkeD – Technology Support

- WiCkeDTM & SPT Design Tool Suites

- Integrated into standard design environments

- For more information and support contact www.muneda.com

SONIX at MUGM MunEDA User Group Meeting 2023

“WiCkeD nominal and feasibility optimization tools helped our R&D to fulfill all constraints, performance specifications at same time and even minimized the area of circuits like a bandgap voltage reference in 90nm technology”

Let’s work together on your

next design project

Use MunEDA tools and support to speed up efficiency,

quality and outcome of your next circuit design project